## IOWA STATE UNIVERSITY Digital Repository

Graduate Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

2008

# Thermal modeling and management of DRAM memory systems

Jiang Lin Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Lin, Jiang, "Thermal modeling and management of DRAM memory systems" (2008). *Graduate Theses and Dissertations*. 10978. https://lib.dr.iastate.edu/etd/10978

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

#### Thermal modeling and management of DRAM memory systems

by

Jiang Lin

## A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Major: Computer Engineering

Program of Study Committee: Zhao Zhang, Major Professor Arun K. Somani Akhilesh Tyagi J. Morris Chang Masha Sosonkina

Iowa State University

Ames, Iowa

2008

Copyright © Jiang Lin, 2008. All rights reserved.

www.manaraa.com

Dedicated to my brother Hui ...

### TABLE OF CONTENTS

| LIST ( | OF TABLES                                                                 | vi  |

|--------|---------------------------------------------------------------------------|-----|

| LIST   | OF FIGURES                                                                | vii |

| CHAP   | TER 1. Introduction                                                       | 1   |

| CHAP   | TER 2. Background                                                         | 4   |

| 2.1    | Thermal Management in Computer Systems                                    | 4   |

| 2.2    | Thermal Issue of DDR2 and Fully Buffered DIMM (FBDIMM) Memories $\ . \ .$ | 5   |

| 2.3    | Dynamic Thermal Management Schemes for Memories                           | 6   |

| 2.4    | DRAM Power Saving Techniques                                              | 7   |

| 2.5    | Other Related Work on Power Savings                                       | 7   |

| CHAP   | TER 3. Power and Thermal Model of DRAM Memory                             | 8   |

| 3.1    | Introduction                                                              | 8   |

| 3.2    | Structure of FBDIMM                                                       | 9   |

| 3.3    | Power Model of FBDIMM                                                     | 11  |

| 3.4    | Isolated Thermal Model of FBDIMM                                          | 14  |

| 3.5    | Integrated Thermal Model of FBDIMM                                        | 17  |

| CHAP   | TER 4. Proposed DTM Schemes and Their Simulation Result                   | 19  |

| 4.1    | Introduction                                                              | 19  |

| 4.2    | Dynamic Thermal Management for FBDIMM Memory                              | 21  |

|        | 4.2.1 Existing Memory DTM Schemes                                         | 21  |

|        | 4.2.2 Proposed DTM Schemes                                                | 21  |

|        | 4.2.3 DTM-ACG and DTM-CDVFS Integrated with Formal Control Method         | 22  |

| 4.3                             | Exper                                                                                               | imental Methodology                                                       | 23                                                 |

|---------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------|

|                                 | 4.3.1                                                                                               | Two-Level Thermal Simulator                                               | 23                                                 |

|                                 | 4.3.2                                                                                               | Workloads                                                                 | 26                                                 |

|                                 | 4.3.3                                                                                               | DTM Parameters                                                            | 27                                                 |

|                                 | 4.3.4                                                                                               | Parameters in PID Formal Controller                                       | 28                                                 |

| 4.4                             | Effect                                                                                              | iveness of Memory DTM Schemes                                             | 28                                                 |

|                                 | 4.4.1                                                                                               | Performance Impact of Thermal Release Point                               | 28                                                 |

|                                 | 4.4.2                                                                                               | Performance Comparison of DTM Schemes                                     | 30                                                 |

|                                 | 4.4.3                                                                                               | Impact on Energy Consumption                                              | 36                                                 |

|                                 | 4.4.4                                                                                               | DTM Interval                                                              | 42                                                 |

| 4.5                             | Impac                                                                                               | t of Thermal Interaction between Processors and DRAM Memory $\ . \ . \ .$ | 42                                                 |

|                                 | 4.5.1                                                                                               | Performance Comparison                                                    | 45                                                 |

|                                 | 4.5.2                                                                                               | Sensitivity Analysis of Thermal Interaction Parameter                     | 45                                                 |

|                                 |                                                                                                     | 5. A Case Study of Memory Thermal Management for Multi-                   |                                                    |

| CHAP                            | IER                                                                                                 | A Case Study of Memory Therman Management for Multi-                      |                                                    |

|                                 |                                                                                                     | ems                                                                       | 48                                                 |

|                                 | e Syst                                                                                              |                                                                           | 48<br>48                                           |

| cor                             | e Syst<br>Introd                                                                                    | ems                                                                       |                                                    |

| <b>cor</b><br>5.1               | e Syst<br>Introd                                                                                    | ems                                                                       | 48                                                 |

| <b>cor</b><br>5.1               | e Syst<br>Introc<br>Design                                                                          | ems                                                                       | 48<br>50                                           |

| <b>cor</b><br>5.1               | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2                                                        | ems                                                                       | 48<br>50<br>50                                     |

| <b>cor</b><br>5.1<br>5.2        | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2                                                        | ems                                                                       | 48<br>50<br>50<br>52                               |

| <b>cor</b><br>5.1<br>5.2        | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2<br>Exper                                               | ems                                                                       | 48<br>50<br>50<br>52<br>56                         |

| <b>cor</b><br>5.1<br>5.2        | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2<br>Exper<br>5.3.1<br>5.3.2                             | ems                                                                       | 48<br>50<br>50<br>52<br>56<br>56                   |

| <b>cor</b><br>5.1<br>5.2<br>5.3 | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2<br>Exper<br>5.3.1<br>5.3.2                             | ems                                                                       | 48<br>50<br>50<br>52<br>56<br>56<br>59             |

| <b>cor</b><br>5.1<br>5.2<br>5.3 | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2<br>Exper<br>5.3.1<br>5.3.2<br>Result                   | ems                                                                       | 48<br>50<br>50<br>52<br>56<br>56<br>59<br>60       |

| <b>cor</b><br>5.1<br>5.2<br>5.3 | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2<br>Exper<br>5.3.1<br>5.3.2<br>Result<br>5.4.1          | ems                                                                       | 48<br>50<br>52<br>56<br>56<br>59<br>60<br>60       |

| <b>cor</b><br>5.1<br>5.2<br>5.3 | e Syst<br>Introd<br>Design<br>5.2.1<br>5.2.2<br>Exper<br>5.3.1<br>5.3.2<br>Result<br>5.4.1<br>5.4.2 | ems                                                                       | 48<br>50<br>52<br>56<br>56<br>59<br>60<br>60<br>63 |

| 5.5 Conclusion                        | 77 |

|---------------------------------------|----|

| CHAPTER 6. Conclusion and Future Work | 78 |

| BIBLIOGRAPHY                          | 79 |

| ACKNOWLEDGMENTS                       | 83 |

#### LIST OF TABLES

| Table 3.1 | The values of parameters in Equation 3.2 for FBDIMM with 1GB            |    |

|-----------|-------------------------------------------------------------------------|----|

|           | DDR2-667x8 DRAM chips made by 110nm process technology                  | 14 |

| Table 3.2 | The value of parameters in the thermal model for the AMB and DRAM       |    |

|           | chips in the given type of FBDIMM used in our simulation. The           |    |

|           | columns in bold type are used in our experiments                        | 16 |

| Table 3.3 | The values of parameters in the thermal model for DRAM ambient          |    |

|           | temperature                                                             | 18 |

|           |                                                                         |    |

| Table 4.1 | Simulator parameters.                                                   | 25 |

| Table 4.2 | Workload mixes.                                                         | 26 |

| Table 4.3 | Thermal emergency levels and their default settings used for the chosen |    |

|           | FBDIMM                                                                  | 27 |

| Table 4.4 | Processor power consumption of DTM schemes                              | 41 |

|           |                                                                         |    |

| Table 5.1 | Thermal emergency levels and thermal running states                     | 53 |

| Table 5.2 | Workload mixes.                                                         | 59 |

vi

## LIST OF FIGURES

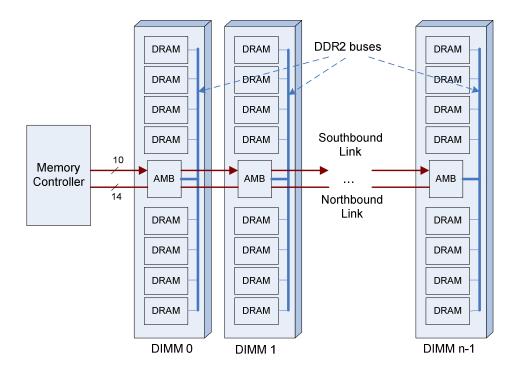

| Figure 3.1  | The structure of Fully-Buffered DIMM with one channel, $\boldsymbol{n}$ DIMMs |    |

|-------------|-------------------------------------------------------------------------------|----|

|             | and eight DRAM chips per DIMM. The memory controller is able to               |    |

|             | connect up to six channels, and each channel may connect up to eight          |    |

|             | DIMMs                                                                         | 9  |

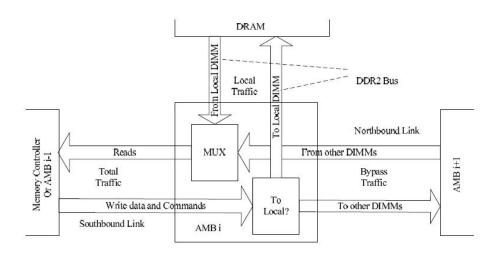

| Figure 3.2  | Four categories of data traffic that flows through AMB                        | 13 |

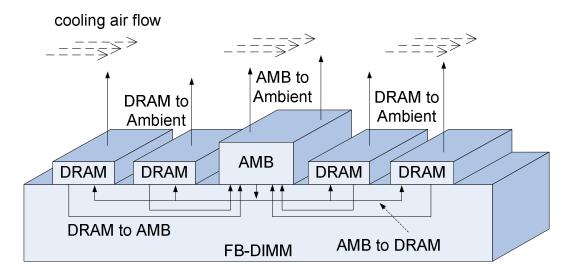

| Figure 3.3  | Heat dissipation of FBDIMM. The arrows represent heat dissipation paths.      | 15 |

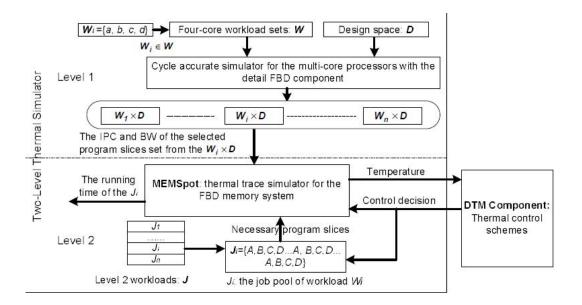

| Figure 4.1  | Two-level thermal simulator                                                   | 24 |

| Figure 4.2  | Performance of DTM-TS with varied TRP. The DRAM TDP is $85.0^{\circ}$ C       |    |

|             | and the AMB TDP is 110.0°C. $\ldots$                                          | 29 |

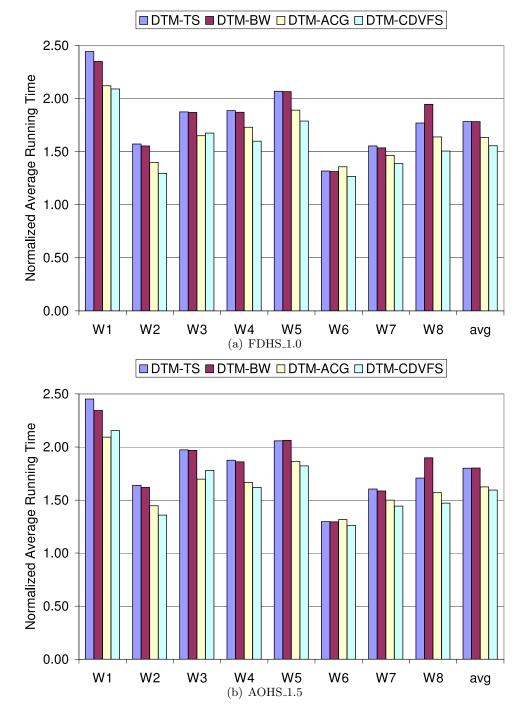

| Figure 4.3  | Normalized running time for DTM schemes                                       | 31 |

| Figure 4.4  | Normalized total memory traffic for DTM schemes                               | 33 |

| Figure 4.5  | AMB temperature changes of DTM-TS for W1 with AOHS_1.5                        | 35 |

| Figure 4.6  | AMB temperature changes of DTM-BW for W1 with AOHS_1.5                        | 36 |

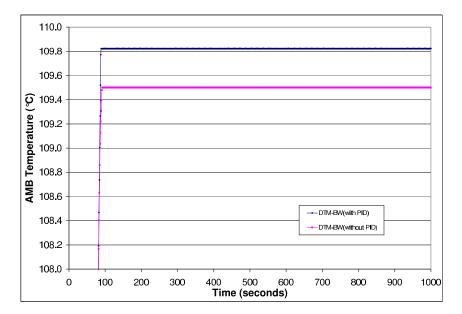

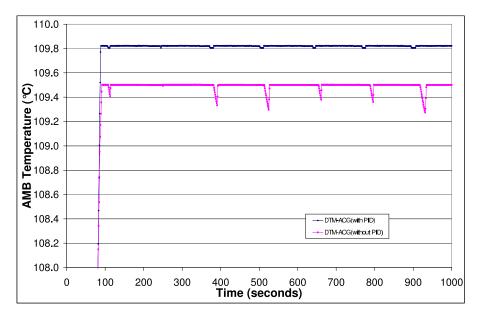

| Figure 4.7  | AMB temperature changes of DTM-ACG for W1 with AOHS_1.5                       | 37 |

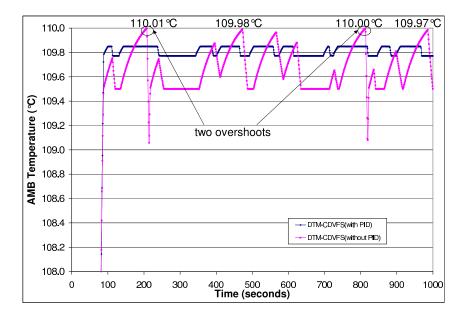

| Figure 4.8  | AMB temperature changes of DTM-CDVFS for W1 with AOHS_1.5. $\ .$              | 38 |

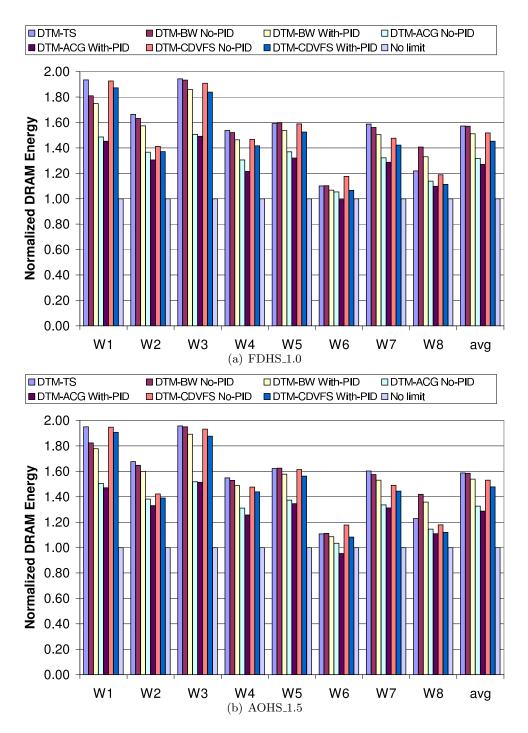

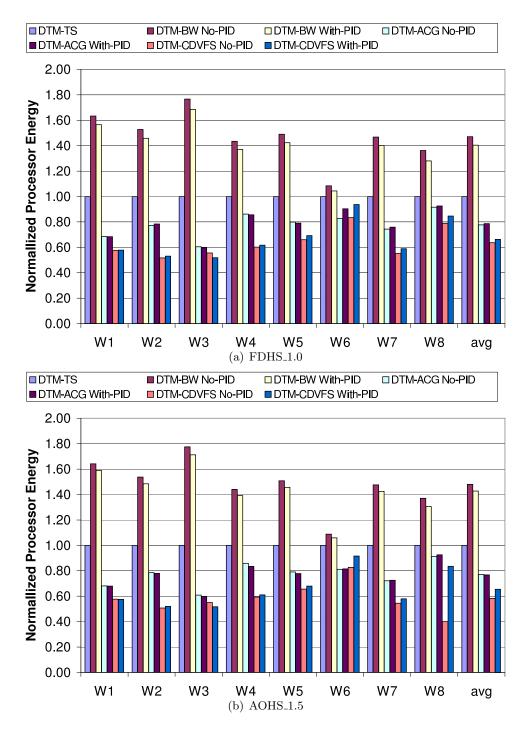

| Figure 4.9  | Normalized energy consumption of FBDIMM for DTM schemes                       | 39 |

| Figure 4.10 | Normalized energy consumption of processors for DTM schemes                   | 40 |

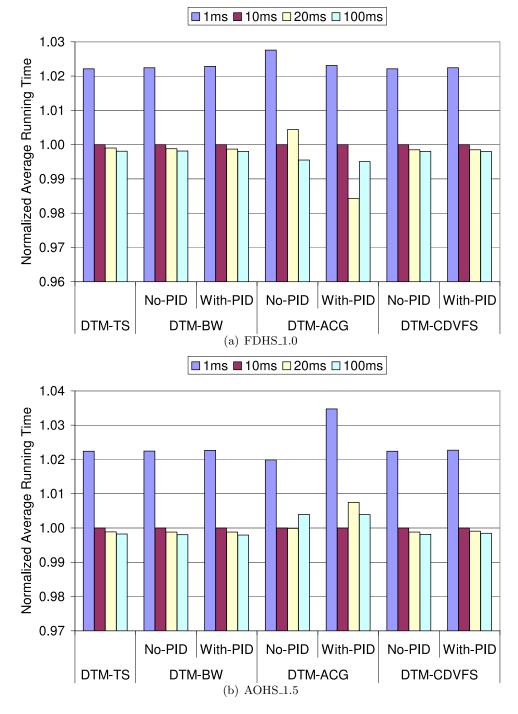

| Figure 4.11 | Normalized average running time for different DTM intervals                   | 43 |

| Figure 4.12 | Normalized running time for DTM schemes                                       | 44 |

| Figure 4.13 | Average normalized running time with different degrees of thermal in-         |    |

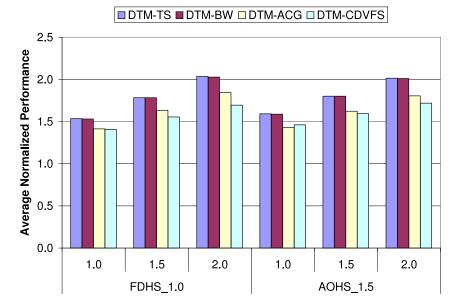

|             | teraction.                                                                    | 46 |

vii

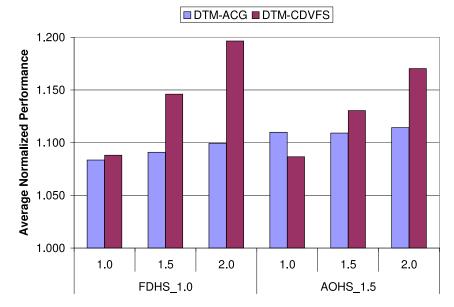

| Figure 4.14 | Average normalized performance improvement of DTM-ACG and DTM-           |    |

|-------------|--------------------------------------------------------------------------|----|

|             | CDVFS with different degrees of thermal interaction, compared with       |    |

|             | DTM-BW                                                                   | 47 |

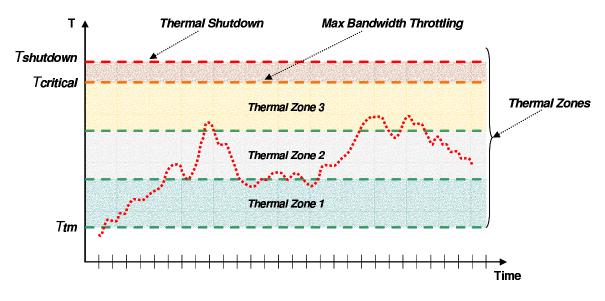

| Figure 5.1  | Thermal Zone                                                             | 50 |

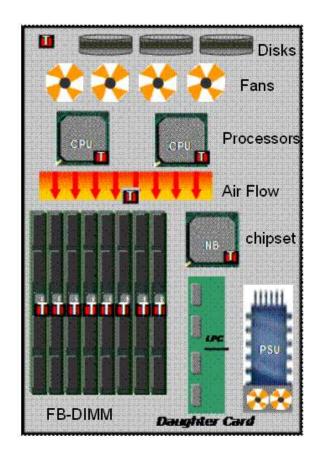

| Figure 5.2  | Intel SR1500AL system with thermal sensors ("T")                         | 57 |

| Figure 5.3  | The daughter card                                                        | 58 |

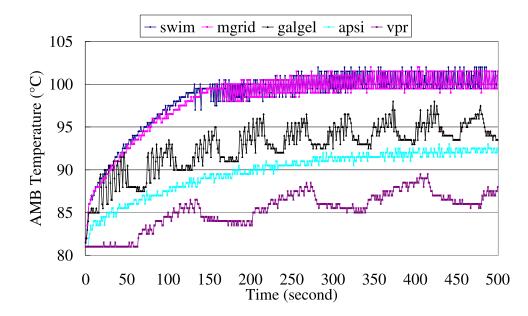

| Figure 5.4  | AMB temperature curve for first 500 seconds of execution                 | 61 |

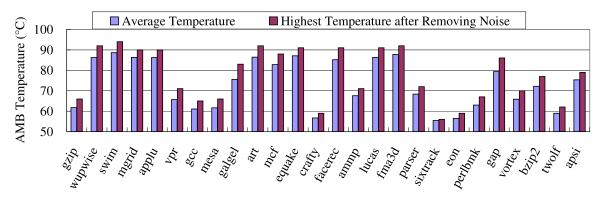

| Figure 5.5  | AMB temperature when memory is driven by homogeneous workloads           |    |

|             | on the PE1950 without DTM control                                        | 62 |

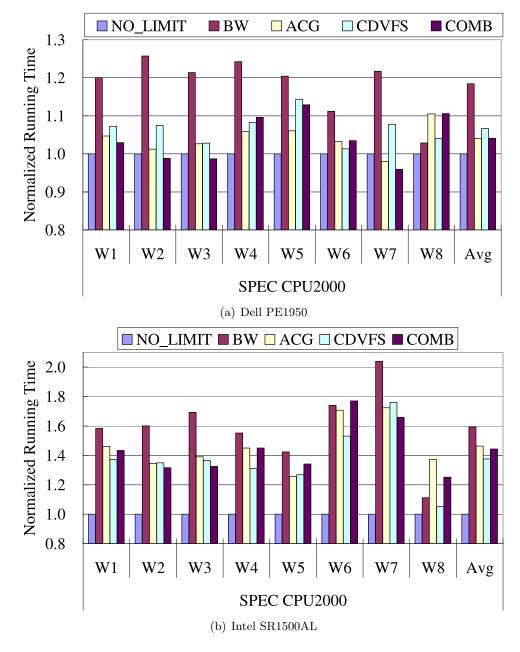

| Figure 5.6  | Normalized running time of SPEC CPU2000 workloads.                       | 64 |

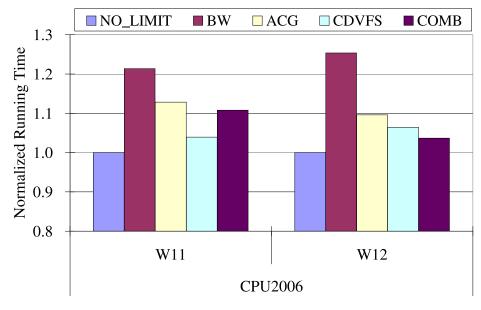

| Figure 5.7  | Normalized running time of SPEC CPU2006 workloads on PE1950              | 66 |

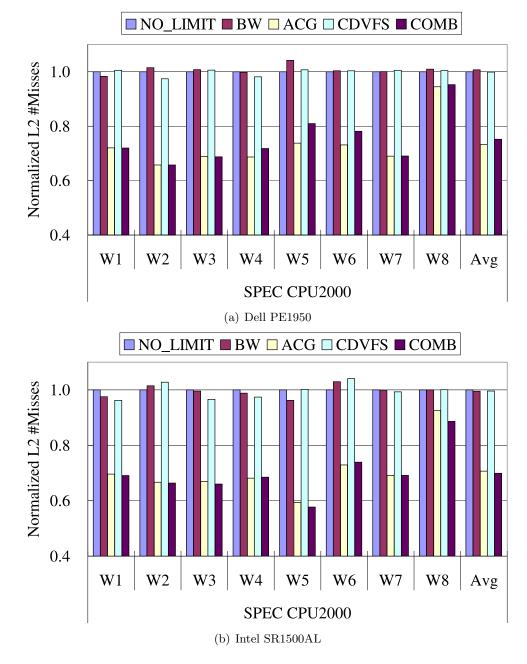

| Figure 5.8  | Normalized numbers of L2 cache misses.                                   | 67 |

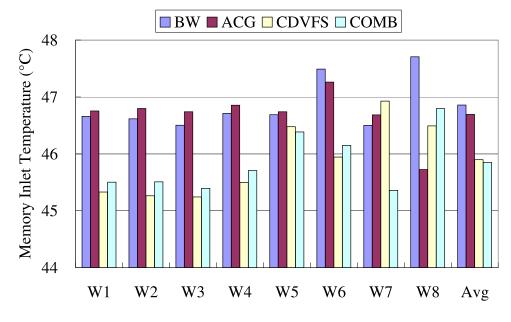

| Figure 5.9  | Measured memory inlet temperature                                        | 70 |

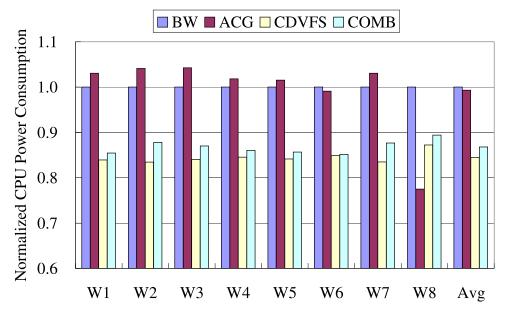

| Figure 5.10 | CPU power consumption.                                                   | 71 |

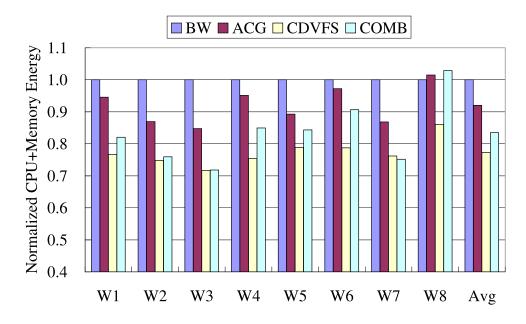

| Figure 5.11 | Normalized energy consumption of DTM policies                            | 72 |

| Figure 5.12 | Normalized running time on Intel SR1500AL at a room system ambient       |    |

|             | temperature (26°C). $\ldots$                                             | 73 |

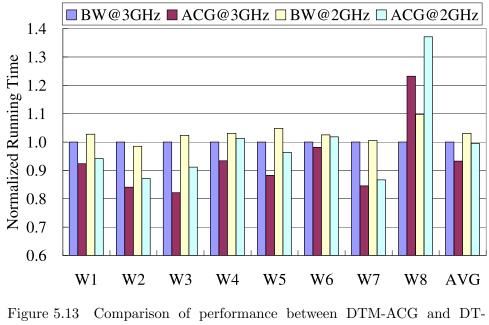

| Figure 5.13 | Comparison of performance between DTM-ACG and DTM-BW under               |    |

|             | two different processor frequencies on Intel SR1500AL                    | 75 |

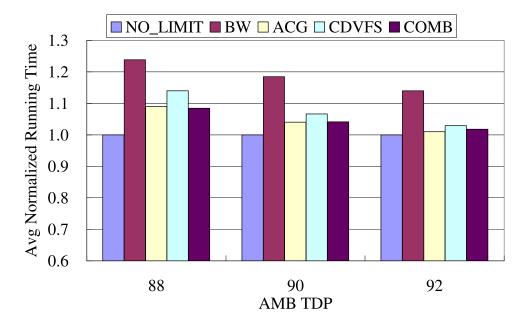

| Figure 5.14 | Normalized running time averaged for all workloads on PE1950 with        |    |

|             | different AMB TDPs                                                       | 76 |

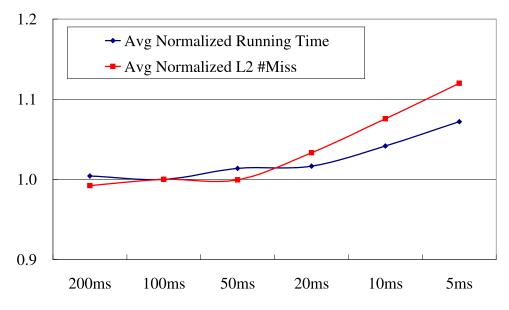

| Figure 5.15 | Normalized running time and number of L2 cache misses averaged for       |    |

|             | all workloads on PE1950 with different switching frequencies. $\ldots$ . | 77 |

#### CHAPTER 1. Introduction

Thermal issues have been first-order considerations in designing processors and hard disk for a long time [3, 52, 54, 12, 27]; and now they are becoming critically important for DRAM memory subsystems as well [26, 33, 31, 32]. This trend is driven by the wide adoption of multi-core processors and their ever increasing demands for high capacity and bandwidth from DRAM memory subsystems.

Current thermal solutions and cooling capabilities of DRAM memories allow full system performance under normal operating conditions. Thermal management is used as a protection mechanism that ensures safe operation and prevents thermal emergencies under abnormal scenarios. These scenarios, while not common, do occur in practice. They can be due to a poorly designed thermal solution, system fan failure, obstructions to airflow within a system, thermally challenging workload mix or other reasons that cause a system to operate outside of its thermal design boundaries. Thermal management is also necessary when users or system operators make a decision to operate in more thermally constrained environments, including reduction of fan speed for acoustic reasons, and operating under high ambient temperatures to reduce cooling costs in data centers. In practice, the use of DRAM thermal management has appeared both in servers [33] and on mobile platforms [26]. In the future, as DRAM power density continues to increase, even advanced cooling features such as fans over DRAM devices, which increases system cooling budget and overall cost, may not allow full system performance under normal operating conditions.

Regardless of the exact reason, a robust thermal management scheme is needed to ensure safe system operation while maximizing its performance under thermal constraints. Instead of fully shutting down the system upon reaching a thermal threshold, a carefully designed

DTM (dynamic thermal management) scheme may improve system performance and/or system power efficiency under the same thermal constraints. Therefore, research on sophisticated DRAM DTM schemes is highly desired.

To address this emerging issue, we have proposed and evaluated two new DTM schemes which take a novel approach different from existing DTM schemes. Instead of throttling memory accesses directly at the memory side upon reaching a thermal threshold, the new approach coordinates DRAM thermal states and processors' running states: when DRAM is in thermal emergency, it slows down the memory access intensity by either gating some processor cores or applying DVFS (dynamic voltage and frequency scaling) on the processor cores. These two new schemes have first been evaluated using simulation and then implemented and evaluated on real systems. Furthermore, to support memory thermal studies, a simple and accurate thermal model is proposed to estimate the dynamic temperature changes of DRAM memory subsystems. A two-level simulator has been developed to emulate the thermal behavior of memory subsystems. The simulation results show that the proposed schemes provide better performance and energy efficiency than existing simple DTM schemes. To confirm the conclusions make by simulation, we have further performed a case study of the proposed DTM schemes through measurement on real systems by implementing the proposed DTM schemes in software and conducted experiments on two server platforms. The measurement-based experiments first confirm that the two proposed schemes significantly improve performance and energy efficiency in real server systems. In addition, we have surprising findings that are hard to get from the simulation approach. In short, we have made a case that, with careful thermal management designs, DRAM thermal issues can be handled at the cost of very small performance penalty.

The rest of this thesis is organized as follows. After discussing the background and related work in Chapter 2, we present our integrated power and thermal model by using existing industrial power and temperature estimation methods in Chapter 3. Chapter 4 demonstrates how we use the simulation approach to study the DRAM thermal issues. Chapter 5 describes the case study of the proposed DTM schemes through measurement on real systems. Finally,

Chapter 6 concludes this thesis and discusses future directions.

#### CHAPTER 2. Background

#### 2.1 Thermal Management in Computer Systems

Thermal management has become a research focus in recent years. Most studies so far have focused on processors, disks, server systems and data centers. Brooks and Martonosi study processor dynamic thermal management (DTM) mechanism, such as scaling the clock frequency or voltage [3]. Skadron et al. develop a thermal model for individual functional blocks using thermal resistances and capacitances derived from the layout of the micro-architecture structures [52]. They further extend the model to HotSpot, which models thermal behavior at the microarchitecture level using a network of thermal resistances and capacitances, and can identify the hottest unit on a chip [54]. They also propose several DTM techniques, such as migrating computation to spare hardware units from overheated ones. Li et al. study the thermal constraints in the design space of CMPs [29]. Donald and Martonosi explore the design space of thermal management techniques for multicore processors [9]. Regarding the DTM for the hard disk drives, Gurumurthi et al. develop models to capture the capacity, performance and thermal behavior of disk drives. They also present two DTM techniques for hard disks, exploiting the thermal slack or throttling disk activities [12]. Kim et al. further develop a performance-temperature simulator of disk drives and study the thermal behaviors and management of storage systems using server workloads [27]. There are also a set of works which study the DTM for server systems and data centers. Moore et al. use a temperatureaware workload placement algorithm to reduce the cooling cost of data centers [43]. Heath et al. propose Mercury, a temperature emulation suite for servers; they also develop and evaluate Freon, a system for managing thermal emergency in server cluster [15]. Choi et al. propose ThermoStat, a CFD-based tool, to study thermal optimization at run time on server systems

as well as the layout optimization in the design phase [6].

## 2.2 Thermal Issue of DDR2 and Fully Buffered DIMM (FBDIMM) Memories

Processor speeds double approximately every eighteen months, while main memory speeds double only about every ten years. These diverging rates resulted in a "memory wall", in which memory accesses dominate program performance. Recently, improvement of single processor performance has slowed down in terms of single thread execution because of increasing power consumption, increasing difficulty in finding enough instruction level parallelism, and increasing relative wire delay and main memory access latency. Instead of building highly complex single-threaded processors, processor designers put multiple processor cores on a single chip to improve the overall throughput. With multicore processors, the high memory access latency is likely to persist. Furthermore, as the number of processor cores increases, multicore processors not only demand fast main memory speed as did single-thread processors, but also require large memory capacity and high aggregate memory bandwidth to support simultaneous multiple executions.

There have been many technology advances to improve DRAM bandwidth and capacity and to address the latency issue. DRAM performance has been improved both in technology and in architecture. In technology, DRAM latency is improved by 7% every year, which is much slower than that of processor. In computer architecture, many architecture-level mechanisms have been employed or studied at the DRAM level to improve performance, such as latency reduction and data transfer rate improving techniques [50, 20, 21, 40, 41, 39, 45, 46], and memory access scheduling [44, 36, 35, 37, 38, 17, 49, 48, 5, 59, 34, 58, 7, 60, 19, 47, 53]. Responding to the demand of improving main memory capabilities from multicore processors, new memory technologies have been introduced by industry to support both large memory capacity and high memory bandwidth, such as fully buffered DIMM (FBDIMM) proposed by Intel [13] and the Socket G3 Memory Extender (G3MX) to be supported by AMD [1]. Both technologies use narrow and high frequency buses to connect DRAM memory with s chipset

or processors. Therefore, the number of pins of each memory channel is reduced and more memory channels can be supported in a system.

However, with those technological advances, DRAM memory subsystem now consumes a significant portion of total system power. At this point, in server systems, DRAM power consumption is comparable to that of processors. Moreover, with increased power consumption, more heat is generated. Consequently, the DRAM thermal problem has become a real issue recently for both DDR2 DRAM and FBDIMM. A recent study has reported that on a mobile system, the temperature of DDR2 DRAM devices may exceed their thermal design point of 85°C when running real workloads at an ambient temperature of 35°C [26]. On sever platforms, the recently deployed FBDIMM has become a focus for DRAM thermal studies [31, 33]. For example, a current small-scale, two-way SMP server [22] provides peak memory bandwidth of 21 GB/s and maximum memory capacity of 32 GB to support up to eight cores. Its maximum DRAM power consumption can reach 100 watts, which can be in the same range of power consumed by the processors. Consequently, DRAM power and thermal management is an urgent and critical issue.

#### 2.3 Dynamic Thermal Management Schemes for Memories

In practice, two DTM schemes have been used to prevent AMB or DRAM device overheating. In *thermal shutdown*, the memory controller (or the operating system) periodically reads the temperature of DIMMs from thermal sensors embedded into DIMMs. If the reading exceeds a preset thermal threshold, the memory controller stops all accesses to the DRAMs until the temperature drops below the threshold by a preset margin. In *bandwidth throttling* [22, 33], the memory controller throttles memory throughput when overheating is to happen. The throttling is done by counting and limiting the number of row activations in a given window of time.

#### 2.4 DRAM Power Saving Techniques

Several studies have focused on reducing the power consumption of main memory systems. Although those proposed techniques may also help in lowering the memory temperature, they do not directly target the alleviation of the memory thermal emergency. Lebeck et al. propose a power-aware page allocation scheme that utilizes the long-latency but low-power DRAM modes. It minimizes the number of memory chips used by an application to increase the possibility that a DRAM chip can be put into low-power modes without affecting overall performance [28]. Delaluz et al. further propose using compiler techniques to map memory pages with similar active periods to the same chips in order to allow DRAM chips to stay in low-power modes longer [8]. Fan et al. study memory controller policies considering DRAM power states for power saving [10]. Huang et al. design and implement power-aware virtual memory management to save power consumption of main memory systems [18].

#### 2.5 Other Related Work on Power Savings

Isci et al. [25] has proposed a runtime phase prediction method and use it to predict memory intensive phases of a program. They further propose the use of DVFS on the processor during those phases to save the power and energy consumption of a single-threaded mobile processor. In DTM-CDVFS, DVFS is triggered by thermal emergency and the objective is to improve performance and power efficiency for multicore server systems. Since memory temperature change is much slower than program phase change, thermal emergency is likely a more reliable trigger for DVFS with a performance target, though phase prediction can work when thermal emergency does not appear. Another study by Isci et al. [24] proposes methods to use per-core DVFS in managing the power budget of a multicore processor. Besides the difference that this study is focused on memory thermal management, per-core DVFS is not yet available on mainstream processors except Intel Itanium (to the best of our knowledge).

#### CHAPTER 3. Power and Thermal Model of DRAM Memory

#### 3.1 Introduction

Our DRAM power and thermal model is presented in this chapter. We focus on systems with fully buffered DIMM (FBDIMM) as the main memory. FBDIMM is designed for multicore processors to meet their demand of high bandwidth and large capacity. However, it has thermal issues when running at the peak performance for a while (usually less than a hundred seconds). It uses narrow and high-speed memory channels, and includes Advanced Memory Buffer (AMB) to buffer and transfer data between memory channels and DDR2 DRAM chips. In FBDIMM, both the AMBs and DRAM chips may be overheated. The power density of an AMB can be as high as  $18.5Watt/cm^2$  [30]. To model the power consumption and thermal behavior of FBDIMM, our model uses two sets of formulas: one by Micron Technology, Inc. for DRAM power consumption [42] and the other by Intel Corp. for AMB and DRAM temperature estimation in a stable state [23]. The heat generated by the AMBs and DRAM chips is determined by the memory throughput. The model estimates the dynamic change of temperatures of the AMBs and DRAM chips using the current memory throughput, which can be collected by simulation or by measurement.

To be discussed in Chapter 5, there are strong thermal interactions between processors and DRAM memory in some server platforms. In these platforms, the cooling air flow is preheated by processors, and then passes through FBDIMM memories. Therefore, the memory inlet (ambient) temperature is affected by heat generated by processor. Our isolated DRAM thermal model does not consider this thermal interaction, while our integrated DRAM thermal model does. The integrated DRAM thermal model estimates DRAM ambient temperature by taking IPCs, voltage supply levels and frequencies of processor cores into consideration.

The rest of this chapter is organized as follows. We first discuss the basic structure of FBDIMM in Section 3.2. We then present our power model of FBDIMM in Section 3.3. Finally, we present the isolated thermal model of FBDIMM in Section 3.4, and the integrated thermal of FBDIMM in Section 3.5.

#### 3.2 Structure of FBDIMM

Figure 3.1 The structure of Fully-Buffered DIMM with one channel, n DIMMs and eight DRAM chips per DIMM. The memory controller is able to connect up to six channels, and each channel may connect up to eight DIMMs.

FBDIMM is designed to scale with multi-core processors in both memory bandwidth and capacity. Today, a DDR2 memory channel using DDR2-800 chips can provide 6.4GB/s bandwidth. However, because of the stub bus structure of DDR2 and DDR3 channels, they can hardly maintain the signal integrity without reducing the number of memory devices (DRAM chips) and the wire length [13]. In other words, the maximum memory capacity per channel may have to drop with the increase of bandwidth. Furthermore, DDR2 or DDR3 channels use

a large number of pins (240 pins for DDR2 DIMM used in desktop computers), which limits the number of channels that can be put on a motherboard.

Figure 3.1 shows the structure of FBDIMM with one channel connecting n DIMMs. It has a two-level interconnect structure, the FBDIMM channel and the DDR2 buses on the DIMMs<sup>1</sup>. The AMB (Advanced Memory Buffer) is a key component in this interconnect structure. The memory controller links to these AMBs through a narrow but high frequency point-to-point bus, forming a daisy chain. Figure 3.1 shows only one channel connected to the memory controller; in real systems, multiple channels can be connected to a single controller. The DRAM chips on a DIMM are connected to the DIMM's AMB; they are not directly connected to the channel bus. The narrow bus runs at a much higher frequency than the DDR2/DDR3 bus, significantly reducing the number of pins needed per memory channel. The number of pins per channel is 69 with a default configuration. In addition, the point-to-point, daisy-chain connection allows a FBDIMM channel to support more DIMMs at the cost of increased latency. More channels and more DIMMs per channel mean the FBDIMM technology can support higher memory capacity. Meanwhile, the use of AMB leaves the DRAM chips unchanged.

The FBDIMM channel interconnect has two unidirectional links, a southbound link and a northbound link, which operate independently. The southbound link has ten logical signals and may carry memory commands and data to be written; and the northbound link typically has fourteen logical signals and carries the read data returned from the DIMMs. Each logical signal is carried by a pair of wires using differential signaling. The memory controller schedules the commands and data transfers on both links. During each memory cycle, the southbound link can transfer three commands or one command and 16-byte write data; and the northbound link can transfer 32-byte read data. The maximum bandwidth of the northbound link matches that of one DDR2 channel. In the future, the FBDIMM will support DIMMs using DDR3 DRAM. A point worth noting is that the overall bandwidth of a FBDIMM channel is higher than that of a DDR2 channel because the write bandwidth is extra.

The AMB is a small logic component attached to each DIMM and sits between the memory

<sup>&</sup>lt;sup>1</sup>Unlike in conventional DDR2 memory, here one bus only connects DRAM chips of only one DIMM.

controller and DRAM chips. It receives commands and data from the FBDIMM channel; and then determines whether the commands and data are for its memory devices or not. If yes, the AMB translates the commands and data from the FBDIMM channel format to the internal DDR2/DDR3 format; otherwise, it forwards the commands and data to the next AMB or the memory controller along the FBDIMM channel. An important feature of the FBDIMM is that it has variable read latency (VRL). The minimum latency of accessing a given DIMM depends on its logic distance from the memory controller. In other words, a DIMM close to the memory controller may provide return data in a shorter latency than a remote DIMM. The FBDIMM can also be configured to not supporting the VRL feature. In that case, every DIMM has a fixed minimum read latency, which is the latency of the farthest DIMM.

#### 3.3 Power Model of FBDIMM

We first develop a power model of FBDIMM, including its DRAM chips and AMBs (with DDR2 bus interconnect). Based on the power model, we will develop a thermal model in Section 3.4. We assume that the FBDIMM uses the close page mode with auto precharge. This configuration achieves better overall performance in multicore program execution than the open page mode or the close page mode without auto precharge. We also assume that the FBDIMM uses 1GB DDR2-667x8 DRAM chips made by 110nm process technology. Additionally, the memory access burst length is fixed at four to transfer a single L2 cache block of 64 bytes over two FBDIMM channels.

A Simple DRAM Power Model We derive a simple power model from a DRAM power calculator [42] provided by Micron Technology, Inc. The DRAM power at a given moment is estimated as follows:

$$P_{\text{DRAM}} = P_{\text{DRAM},\text{static}} + \alpha_1 \times \text{Throughput}_{\text{read}} + \alpha_2 \times \text{Throughput}_{\text{write}}$$

(3.1)

We assume that the DRAM does not enter low power modes and on average during 20% of time the DRAM banks of a DIMM are all precharged. This is a representative setting and

is used as the default setting by the power calculator. With these assumptions, the DRAM static power can be estimated as a constant for a relatively long time interval, e.g. a few milliseconds<sup>2</sup>. The value is 0.98 Watt for a single FBDIMM, derived by the DRAM power calculator. In the calculator, this value includes the power for DRAM refreshing, although that part is actually dynamic power consumption.

The second and third components belong to the dynamic DRAM power consumption, and are determined by the read throughput, write throughput and row buffer hit rate. With the close page mode and auto-precharge, each DRAM read or write causes three DRAM operations: row activation (RAS), column access (CAS) and precharge (PRE). Each row activation consumes the same amount of energy, and so does each precharge. A column access of a read, however, consumes slightly less power than that of a write. The row buffer hit rate is zero with the close page mode and auto-precharge, therefore it does not appear in Equation 3.1. The value of  $\alpha_1$  is 1.12 Watt/(GB/s) and that of  $\alpha_2$  is 1.16 Watt/(GB/s) for a single FBDIMM, derived from the DRAM power calculator. Finally, the read and write throughput are collected in the simulation.

**AMB Power Modeling** To calculate the AMB power consumption, we first discuss how AMB works. The FBDIMM channel interconnect has two unidirectional links located in the AMBs, a southbound link and a northbound link, which operate independently. The southbound link carries commands and data to be written; and the northbound link carries the read data returned from the DIMMs. As shown in Figure 3.2, the AMB is a small logic component attached to each DIMM and sits between the memory controller and DRAM chips. It receives commands and data from the FBDIMM bus; and then determines whether the commands and data are for its memory devices or not. If the answer is yes, the AMB translates the commands and data to the internal DDR2/DDR3 format; otherwise, it will forward the commands and data to the next AMB or the memory controller through the FBDIMM channel.

An AMB consumes energy in each local request (directed to the local DRAMs), and in each bypassed request (to other DIMMs). For each local read request, the AMB consumes

<sup>&</sup>lt;sup>2</sup>If all DRAM banks of a DIMM are precharged, the static power is lower than otherwise by a small margin.

Figure 3.2 Four categories of data traffic that flows through AMB.

energy in decoding and forwarding the commands to the local DDR2 bus, and then receiving the read data and sending them back through the FBDIMM channel. For each local write, the AMB decodes the commands from FBDIMM channel, and then sends them with data through the local DDR2 bus. For each bypassed read request, the AMB passes the commands through the southbound link and later passes the data through the northbound link. For each bypassed write request, the AMB passes the command and data through the southbound link. For each write request, the AMB passes the command and data through the southbound link. The number of commands and the amount of data transferred are the same for a read or a write request. Therefore, we assume that each local read or write request consumes the same amount of energy, and so does each bypassed read or write request. A local request consumes more energy than a bypassed request.

Based on the above analysis, we model the AMB power consumption as a linear function of memory throughput of bypass traffic and local traffic:

$$P_{\text{AMB}} = P_{\text{AMB\_idle}} + \beta \times \text{Throughput}_{\text{Bypass}} + \gamma \times \text{Throughput}_{\text{Local}}$$

(3.2)

$P_{\text{AMB-idle}}$  represents the power consumption when there is no memory traffic presented to

the AMB. We derive the values of  $P_{AMB,idle}$  and coefficients  $\beta$  and  $\gamma$  from Intel specification [23] for FBDIMM. The values are shown in Tables 3.1.  $P_{AMB,idle}$  has two possible values, 4.0 Watts for the last AMB of an FBDIMM channel and 5.1 Watts for other AMBs. The difference exists because the memory controller and the AMBs must keep in synchronization all the time, which consumes power, while the last AMB only needs to synchronize with one side. The bypass and local throughout is collected in the simulation.

| Parameters                           | Value             |

|--------------------------------------|-------------------|

| $P_{\text{AMB-idle}}$ (last DIMM)    | 4.0 watt          |

| $P_{\text{AMB\_idle}}$ (other DIMMs) | 5.1  watt         |

| β                                    | 0.19  watt/(GB/s) |

| $\gamma$                             | 0.75  watt/(GB/s) |

Table 3.1The values of parameters in Equation 3.2 for FBDIMM with 1GBDDR2-667x8DRAM chips made by 110nm process technology.

#### 3.4 Isolated Thermal Model of FBDIMM

We build a simple thermal model for FBDIMM based on the power model above. First of all, because the DIMMs in FBDIMM memory are "far" from each other and cooling air flow passes through the space between them, we assume that there is no thermal interaction between any two DIMMs. The focus is the thermal behavior of a single DIMM, including the thermal interactions between the DRAM chips and the AMB. Our analysis is based on a previous analysis done by Intel [33], which models the stable temperature of FBDIMM. Our model extends to the dynamic temperature of FBDIMM. As discussed in the introduction of this chapter, the isolated thermal model assumes the memory inlet (ambient) temperature does not change.

We first describe the modeling of stable temperatures of the AMB and DRAMs, i.e. the temperatures if the memory throughput does not change. For a general physical system with heat source and sink, the stable temperature is the balance point where the heat generating speed equals to the heat dissipation speed. The higher the temperature, the faster the heat dissipation speed. Figure 3.3 shows the heat dissipation paths in a single DIMM. The heat

Figure 3.3 Heat dissipation of FBDIMM. The arrows represent heat dissipation paths.

generated by AMB is dissipated along two paths: one to the heat spreader and then to ambient, and another down to the raw card (DIMM board). Similarly, the heat from each DRAM chip has these two dissipation paths, but may or may not have the heat spreader in the first path. Thermal interactions exist among the AMB and DRAMs through the raw card.

The AMB and DRAMs have different stable temperatures<sup>3</sup> that are affected by several factors. First, the heat generation of the AMB and DRAM is determined by the memory throughput. Second, the higher the velocity of the cooling air flow, the quicker the heat dissipation from the AMB and DRAMs to the ambient. Third, the type of heat spreader can change the distribution of heat dissipation between the two paths. There are two types of heat spreader for FBDIMM: AMB Only Heat Spreader (AOHS) and Full DIMM Heat Spreader (FDHS) [30]. The AOHS only contacts and covers the AMB. The FDHS covers the full length of the DIMM including the AMB and DRAMs, providing another channel for the thermal interactions between AMB and DRAMs. One can expect that the difference between stable AMB temperature and the DRAM temperature of DIMMs with FDHS is smaller than that with AOHS. Finally, the ambient temperature affects the stable temperatures: The higher the

<sup>3</sup>The AMB has a higher thermal limit than the DRAMs.

| Heat spreader type                        | AOHS (on AMB) |     | FDHS (on DIM |     | DIMM) |     |

|-------------------------------------------|---------------|-----|--------------|-----|-------|-----|

| Air velocity(m/s)                         | 1.0           | 1.5 | 3.0          | 1.0 | 1.5   | 3.0 |

| $\Psi_{AMB}(^{\circ}C/W)$                 | 11.2          | 9.3 | 6.6          | 8.0 | 7.0   | 5.5 |

| $\Psi_{\rm DRAM\_AMB}(^{\circ}{\rm C/W})$ | 4.3           | 3.4 | 2.2          | 4.4 | 3.7   | 2.9 |

| $\Psi_{\rm DRAM}(^{\circ}{\rm C/W})$      | 4.9           | 4.0 | 2.7          | 4.0 | 3.3   | 2.3 |

| $\Psi_{AMB\_DRAM}(^{\circ}C/W)$           | 5.3           | 4.1 | 2.6          | 5.7 | 4.5   | 2.9 |

| $\tau_{\rm AMB}$ (seconds)                | 50            |     |              |     |       |     |

| $\tau_{\rm DRAM}({\rm seconds})$          | 100           |     |              |     |       |     |

Table 3.2The value of parameters in the thermal model for the AMB and<br/>DRAM chips in the given type of FBDIMM used in our simula-<br/>tion. The columns in bold type are used in our experiments.

ambient temperature, the higher the stable temperatures.

We use the following two equations to calculate the stable temperatures, which are simplified versions of the Intel study [33].

$$T_{\rm AMB} = T_{\rm A} + P_{\rm AMB} \times \Psi_{\rm AMB} + P_{\rm DRAM} \times \Psi_{\rm DRAM\_AMB}$$

(3.3)

$$T_{\rm DRAM} = T_{\rm A} + P_{\rm AMB} \times \Psi_{\rm AMB} - D_{\rm RAM} + P_{\rm DRAM} \times \Psi_{\rm DRAM}$$

(3.4)

Parameter  $T_A$  is the ambient temperature. Parameter  $\Psi_{AMB}$  is the thermal resistance from the AMB to the ambient; thermal resistance is the ratio of the change of stable temperature over the change of power consumption.  $\Psi_{DRAM}$  is the thermal resistance from a DRAM chip to the ambient. Parameters  $\Psi_{AMB,DRAM}$  and  $\Psi_{DRAM,AMB}$  are the thermal resistances from AMB to DRAM and from DRAM to AMB, respectively. The power density and heat generation of the AMB are much higher than those of the DRAM. Therefore, we are only concerned with the chip(s) next to the AMB, which has the highest temperature. The values of those parameters are from the Intel study and listed in Table 3.2. To limit the experimental time, we choose two cooling configurations in this study: AOHS+1.5m/s (AOHS\_1.5) and FDHS+1.0m/s (FDHS\_1.0).

We now model the dynamic temperature changes with varying memory throughput in program execution. We use the following equation to describe the dynamic temperature:

$$T(t + \Delta t) = T(t) + (T_{\text{stable}} - T(t))(1 - e^{-\frac{\Delta t}{\tau}})$$

(3.5)

Basically, the equation treats the temperature in a thermal system like the voltage in an electrical RC circuit. This idea has been used in previous studies [52, 54] and the formula above is based on a classic equation for the electrical RC circuit [14]. In this equation,  $\tau$  is the time for the temperature difference to be reduced by 1/e, i.e.  $T(t+\tau) - T(t) = (1 - 1/e)(T_{\text{stable}} - T(t))$ , if the heat generation rate is a constant. We obtain the value of  $\tau$  for the AMB and DRAMs by observing their temperature changes in a physical testing environment using the same type of FBDIMM as in our simulation environment. It is rounded to an integer number of seconds.

Because the leakage power is negligible for DRAM devices and AMBs, we do not include the thermal-leakage feedback loop in the equation. In other words, we assume their leakage power rate does not increase with the temperature. In an experimental testbed of FBDIMM memory subsystem, we observed only a 2% increase of power rate as the DRAM subsystem heated up. Additionally, the model can be adapted to other DRAMs because the power profiles of various DRAMs are fairly consistent, across both manufacturers and generations.

#### 3.5Integrated Thermal Model of FBDIMM

The thermal model discussed in Section 3.4 assumes a constant memory ambient temperature. In practice, as will be discussed in Chapter 5, this assumption is not true in the systems with strong interactions between DRAM memory and other components. In some systems, the cooling air flow is pre-heated by processors before it passes DRAM memory. This thermal interaction between processors and memory is a significant factor that could not be ignored.

We take a similar approach to model memory ambient temperature as we model DRAM temperature. We use equation 3.6 to model the stable DRAM ambient temperature:

$$T_{\text{A-stable}} = T_{\text{Inlet}} + \Psi_{\text{CPU}_{\text{MEM}}} \times \sum_{i=0}^{N-1} (\xi \times V_{\text{core}_i} \times \text{IPC}_{\text{core}_i})$$

(3.6)

#### www.manaraa.com

|                               | System inlet temperature                         | $\Psi_{\rm CPU\_MEM} \times \xi$ |

|-------------------------------|--------------------------------------------------|----------------------------------|

| Isolated DRAM thermal model   | $FDHS_{1.0:45^{\circ}C}; AOHS_{1.5:50^{\circ}C}$ | 0.0                              |

| Integrated DRAM thermal model | $FDHS_{1.0:40}^{\circ}C; AOHS_{1.5:45}^{\circ}C$ | 1.5                              |

Table 3.3 The values of parameters in the thermal model for DRAM ambient temperature.

The equation models how processors' heat generation affects memory ambient temperature if the heat generation rate stays constant. Parameter  $T_{\text{Inlet}}$  is the inlet temperature of the whole system.  $V_{\text{core},i}$  is voltage supply level of the processor core i and IPC<sub>core,i</sub> is IPC (Instructions Per Cycle) of processor *i*. We use  $(\xi \times V_{\text{core}_i} \times \text{IPC}_{\text{core}_i})$  to model the power consumption of processor core i. The  $(\xi \times IPC)$  estimates the electrical current level of the processor core. Here the IPC is defined as number of committed instructions divided by number of reference cycles. Although the frequencies of the processor cores are not constant with some DTM schemes, the reference cycle time is a constant value which is the cycle time with highest possible frequency of the processor core.  $\Psi_{CPU,MEM}$  is the thermal resistance from the processors to DRAM memory. Table 3.3 lists values of parameters in estimating DRAM memory ambient temperature. In the isolated DRAM thermal model, the heat generated by processors does not affect the DRAM ambient temperature. Therefore, we set  $\Psi_{\text{CPU}}$  to 0.0. We set the value of  $\Psi_{\text{CPU}} \times \xi$ to 1.5 based on our measurement data from real systems. To model a thermal constraint environment, we set system inlet temperature to 45°C for the isolated DRAM thermal model and to 40°C for the integrated DRAM thermal model under configuration FDHS\_1.0. We set them to 50°C and 45°C under configuration AOHS\_1.5.

After getting the  $T_{\text{A-stable}}$ , we use equation 3.5 to model the dynamic temperature behavior of DRAM memory ambient temperature. The thermal RC delay  $\tau_{\text{CPU}}$ \_DRAM(seconds) is 20 seconds in our model. The 20 seconds is an estimated value based on our experiment data on real systems.

#### CHAPTER 4. Proposed DTM Schemes and Their Simulation Result

#### 4.1 Introduction

Recently, simple DTM techniques have been applied in notebook computers with DDR2 memories. Two simple DTM schemes have been used so far for DRAM memories: thermal shutdown and memory bandwidth throttling. Upon detected overheating of DRAM chips, with thermal shutdown, the memory controller stops all memory transactions and shuts down the DRAM chips until they are cooled down. With memory bandwidth throttling, the memory controller lowers bandwidth to reduce DRAM activities. However, abrupt thermal shutdown or bandwidth throttling will make the program execution fluctuate. Intuitively, the program execution is far from optimal for a given thermal envelope: Thermal shutdown frequently stops the memory subsystem and consequently forces the processor to stall; and simple memory bandwidth throttling reduces the memory throughput while the processor, power supply and other components will not be optimal.

In this chapter, we take a new approach that controls the memory throughput by directly controlling the source that generates memory activities – the processor, when the memory thermal envelope is approached. We propose two new schemes and evaluate their effectiveness on systems with multicore processors and Fully Buffered DIMM (FBDIMM) memories [11]. The first scheme, *Adaptive Core Gating*, applies clock gating on selected processor cores according to the DRAM thermal state. The second scheme, *Coordinated DVFS* (dynamic voltage and frequency scaling), scales down the frequency and voltage levels of all processor cores, when the memory is about to be overheated. Using the isolated DRAM thermal model discussed in Section 3.4, our simulation results show that both schemes maintain the memory throughput

as high as allowed by the current thermal limit; and therefore improve the average memory performance. Adaptive core gating further reduces L2 cache conflicts, which leads to lower memory traffic and fewer DRAM bank conflicts. It improves the performance of multiprogramming workloads of SPEC2000 programs by up to 29.6% (18.5% on average) on a four-core processor when compared with the simple thermal shutdown for a configuration used in our study. Coordinated DVFS also reduces memory traffic slightly because the processor generates fewer speculative memory accesses when running at a lower frequency. In addition, the processor power efficiency is improved with voltage scaling. The scheme improves performance 3.6% on average, and may save the processor energy consumption by 36.0% on average, compared with the simple thermal shutdown.

We further use a PID (Proportional-Integral-Differential) method based on formal control theory to improve the efficiency of the proposed DTM schemes. It can make the system temperature to converge quickly to the target temperature, and further improve the performance of adaptive core gating by up to 33.5% (21.4% on average) and coordinated DVFS by 8.3% on average when compared with the simple thermal shutdown.

For the systems with strong thermal interaction between processors and DRAM memory, we use the integrated DRAM thermal model discussed in Section 3.5 to model the dynamic temperature changes of FBDIMM. The simulation results indicate that, beside adaptive core gating, coordinated DVFS also improves system performance significantly in these systems. The adaptive core gating scheme improves the performance of the multiprogramming workloads by 9.1% on average when compared with the simple bandwidth throttling scheme for a configuration used in our study on these systems. The coordinated DVFS has better performance under same configurations. It improves performance by 14.6% on average. The root cause of significant performance improvement of the coordinated DVFS scheme is that it can reduce heat generated by processors largely. Therefore, In a system with the strong thermal interaction, the DRAM ambient temperature is much lower when coordinated DVFS scheme is deployed.

The rest of this chapter is organized as follows. Section 4.2 describes the existing and

proposed DTM schemes for DRAM main memory. Section 4.3 describes the experimental environment. Section 4.4 and Section 4.5 present the results of our experiments.

#### 4.2 Dynamic Thermal Management for FBDIMM Memory

In this section, we first discuss existing DTM schemes for main memory, and then describe our DTM schemes and the use of a formal control method. All DTM schemes assume that thermal sensors are used to monitor the DRAM temperature; and for FBDIMM, the AMBs have already integrated thermal sensors.

#### 4.2.1 Existing Memory DTM Schemes

In thermal shutdown, the memory controller (or the operating system) periodically reads the temperature of DRAMs from the thermal sensors. The period may be a fraction of second. If the temperature exceeds a preset thermal threshold, the memory controller stops all accesses to the DRAMs. The controller keeps checking the temperature periodically and resumes DRAM accesses when the temperature drops below the threshold by a preset margin. In *bandwidth throttling* [33], multiple thermal emergency levels are used to indicate how close the DRAM temperature is to the preset threshold. The BIOS (or the memory controller or OS) periodically reads the temperature, evaluates the thermal emergency level, and decides a memory traffic limit for the current period. Then, the memory controller will enforce this traffic limit. In the rest of this paper, we refer these two schemes as DTM-TS and DTM-BW, respectively.

#### 4.2.2 Proposed DTM Schemes

We propose adaptive core gating (DTM-ACG) and coordinated dynamic voltage and frequency scaling (DTM-CDVFS) schemes. The two schemes are designed for multicore processors. Unlike DTM-TS and DTM-BW that control memory throughput locally at the memory side, the two schemes directly control the multicore processor to affect the memory throughput. For a processor of N cores, DTM-ACG may shut down 1 to N cores adaptively according to the current thermal emergency level. The core shutdown is to apply clock gating, i.e. stop the

clock signal to the specific core. To ensure fairness among benchmarks running on different cores, the cores can be shut down in a round-robin manner. By shutting down some cores, memory throughput is expected to decrease and so is the DRAM and AMB heat generation rate. DTM-CDVFS may lower the frequency and voltage levels of all cores according to the DRAM/AMB thermal emergency level. In other words, it directly links the DRAM/AMB thermal level to the processor frequency and voltage level. In the highest thermal emergency level, for both DTM-ACG and DTM-CDVFS, the memory will be fully shut down. The two schemes may be implemented in OS or memory controller.

Both schemes may make the program execution running more smoothly than DTM-TS and DTM-BW, which shut down the memory system or reduce the bandwidth without considering the processor execution. DTM-ACG has another advantage for multicore processors with shared L2/L3 caches: By reducing the number of active cores, it reduces L2/L3 cache contention and therefore the total number of cache misses. Consequently, the total amount of memory traffic will be reduced and less heat will be generated. DTM-CDVFS has another advantage of its own: It may improve the processor energy efficiency significantly by *proactively* putting the processor in a power mode in coordination with the current DRAM thermal limit. With DTM-BW, a passive DVFS policy at the processor side will not respond in a timely manner because of the relatively long delay in power mode switch with DVFS. With DTM-CDVFS, however, the processor power mode will be switched proactively when the change of memory throughput limit is foreseen.

#### 4.2.3 DTM-ACG and DTM-CDVFS Integrated with Formal Control Method

We further apply a formal control theory method called PID (Proportional-Integral-Differential) into DTM-ACG and DTM-CDVFS schemes. The PID method has recently been used in the processor thermal control [52, 54, 56, 57, 9]. A PID controller uses the following equation:

$$m(t) = K_c \left( e(t) + K_I \int_0^t e(t)dt + K_D \frac{de}{dt} \right)$$

(4.1)

The equation has three components on the right-hand side: the proportional factor, the

integral factor and the differential factor. At any time t, e(t) is the difference between the target temperature and the measured temperature;  $K_c$ ,  $K_I$  and  $K_D$  are proportional, integral and differential constants that are tuned for the specific system; and proper control actions will be taken according to the controller output m(t). The control action is application-dependent; for example, to set the processor frequency according to the range of m(t). The setting of the ranges and the mapping of each range to a control decision are also application-dependent. For DTM-ACG, the control action is to set the processor frequency and voltage levels. We use two PID controllers, one for the AMB thermal control and another for the DRAM thermal control. For any given configuration that we have studied, either DRAM or AMB is always the thermal limit during program execution. The action by the corresponding PID controller will be taken.

The advantages of using the PID formal controller in thermal control is two-fold: First, the robust PID controller may make the temperature to converge to the target temperature within a guaranteed time limit; and the target temperature can be set close to the thermal limit to minimize the performance loss. Second, by taking into account of the history information in the integral factor and the future prediction in the differential factor, the PID controller can smooth the application running by proper control decisions from quantifying the temperature feedback [52, 9].

#### 4.3 Experimental Methodology

#### 4.3.1 Two-Level Thermal Simulator

It takes a relatively long time for the AMB and DRAM to overheat, usually tens of seconds to more than one hundred seconds<sup>1</sup>. Therefore, we need to evaluate the DRAM DTM schemes for at least thousands of seconds. Direct cycle-accurate simulation for studying DRAM thermal management is almost infeasible at this time length. To address this issue, we propose and implement a two-level simulation infrastructure as shown in Figure 4.1. The first-level is a cycle-accurate architectural simulator, which is used to build traces with performance and

<sup>&</sup>lt;sup>1</sup>By comparison, a processor may overheat in tens of milliseconds.

Figure 4.1 Two-level thermal simulator.

memory throughput information for all possible running combinations of workloads under each DTM design choice. The second level simulator emulates the power and thermal behavior of memory systems using those traces. The traces use a 10ms time window, which is sufficient time to capture the fluctuation of temperature. DRAM temperature fluctuates slowly, up to two degrees Celsius per second as we observed on real machines.

As for the first-level simulation, we use M5 [2] as the base architectural simulator and extend its memory part to include a memory simulator for multi-channel FBDIMM with DDR2 DRAM devices. The details of FBDIMM northbound and southbound links and isolated command and data buses inside FBDIMM are simulated, and so are DRAM access scheduling and operations at all DRAM chips and banks. Table 4.1 shows the major parameters of the pipeline, the memory system, the DTM techniques and the DRAM operations. The outputs of the simulator are the traces of the processor performance and memory throughput of each workload  $W_i$  under the entire explored design space D, including varied memory bandwidth, processor running speed and voltage level, and the number of active processor cores. The set of all traces  $W_i \times D$ is then fed into the second-level simulator for power and thermal simulation.

| Parameters              | Values                                                                    |  |

|-------------------------|---------------------------------------------------------------------------|--|

| Processor               | 4-core, 4-issue per core, 21-stage pipeline                               |  |

| Clock frequency scaling | 3.2GHz at 1.55V, 2.8GHz at 1.35V,                                         |  |

|                         | $1.6\mathrm{GHz}$ at $1.15\mathrm{V},0.8\mathrm{GHz}$ at $0.95\mathrm{V}$ |  |

| Functional units        | 4 IntALU, 2 IntMult, 2 FPALU, 1 FPMult                                    |  |

| ROB and LSQ size        | ROB 196, LQ 32, SQ 32                                                     |  |

| Branch predictor        | Hybrid, $8k$ global + $2K$ local, 16-entry RAS                            |  |

|                         | 4K-entry and 4-way BTB                                                    |  |

| L1 caches (per core)    | 64KB Inst/64KB Data, 2-way, 64B line                                      |  |

|                         | hit latency: 1 cycle Inst/3-cycle Data                                    |  |

| L2 cache (shared)       | 4MB, 8-way, 64B line, 15-cycle hit latency                                |  |

| MSHR entries            | Inst:8, Data:32, L2:64                                                    |  |

| Memory                  | 2 logic (4 physical) channels, 4 DIMMs/physical channel                   |  |

|                         | 8 banks/DIMM                                                              |  |

| Channel bandwidth       | 667MT/s (Mega Transfers/second), FBDIMM-DDR2                              |  |

| Memory controller       | 64-entry buffer, 12ns overhead                                            |  |

| Cooling configuration   | AOHS with 1.5m/s cooling air velocity                                     |  |

|                         | and FDHS with 1.0m/s cooling air velocity                                 |  |

| DTM parameters          | DTM interval 10ms, DTM control overhead $25\mu s$                         |  |

|                         | DTM control scale $25\%$                                                  |  |

| Major DRAM parameters   | (5-5-5) : active to read tRCD 15ns,                                       |  |

|                         | read to data valid tCL 15ns, precharge to active tRP 15ns $$              |  |

| Other DRAM parameters   | tRAS=39ns, tRC=54ns, tWTR=9ns, tWL=12ns                                   |  |

|                         | tWPD=36ns, tRPD=9ns, tRRD=9ns                                             |  |

Table 4.1 Simulator parameters.

The second-level simulator, MEMSpot, uses the power and thermal models described in Chapter 3 to emulate the power and thermal behavior of the DRAM chips and AMBs in the FBDIMM memory system. The memory throughput values used in the models are provided by the first-level simulator. The values of other parameters are given in Chapter 3. The MEMSpot simulates the change of DRAM/AMB temperatures using those parameters for the current processor running mode, e.g. the frequency and voltage level. The temperature data are used by the DTM component, which makes control decisions and informs the MEMSpot any changes of processor running mode.

| Workload | Benchmarks                   |

|----------|------------------------------|

| W1       | swim, mgrid, applu, galgel   |

| W2       | art, equake, lucas, fma3d    |

| W3       | swim, applu, art, lucas      |

| W4       | mgrid, galgel, equake, fma3d |

| W5       | swim, art, wupwise, vpr      |

| W6       | mgrid, equake, mcf, apsi     |

| W7       | applu, lucas, wupwise, mcf   |

| W8       | galgel, fma3d, vpr, apsi     |

Table 4.2 Workload mixes.

#### 4.3.2 Workloads

Each processor core is single-threaded and runs a distinct application. From the SPEC2000 benchmark suite [55], we select twelve applications that require high memory bandwidth when the four-core system runs four copies of the application. Eight of them get memory throughput higher than 10GB/s, *swim, mgrid, applu, galgel, art, equake, lucas* and *fma3d*. The other four get memory throughput between 5GB/s and 10GB/s, *wupwise, vpr, mcf* and *apsi*. Then we construct eight multiprogramming workloads randomly from these selected applications as shown in Table 4.2.

In order to observe the memory temperature characteristics in the long run, the secondlevel simulator runs the multiprogramming workloads as batch jobs. For each workload W, its corresponding batch job J mixes multiple copies (fifty in our experiments) of every application  $A_i$  contained in the workload. When one application finishes its execution and releases its occupied processor core, a waiting application is assigned to the core in a round-robin way. In order to limit the simulation time of the first-level architectural simulator while still getting the accurate behavior of a program's execution, each application is approximated by replicas of a representative program slice of 100 million instructions picked up according to SimPoint 3.0 [51]. To determine the number of replicas for each application, we use the simulator sim-safe from the SimpleScalar 3.0 suite [4] to get the total number of instructions of each application and then divide it by 100 million. Using this approach, we are able to simulate the execution

of a batch job with actual running time of thousands of seconds within a few days. This allows us to balance between the simulation accuracy and time, and to explore a wide design space of DTM schemes.

#### 4.3.3 DTM Parameters

The thermal limits for the AMB and DRAM chips are 110°C and 85°C, respectively, for the FBDIMM with 1GB DDR2-667x8 DRAM we chose in this study [23]. We define five thermal emergency levels, L1 to L5 for the DTM schemes as shown in Table 4.3. DTM-TS keeps the memory system turned on in states L1/L2 and keeps it shut down in state L5. As for states L3/L4, DTM-TS shuts down the memory system when the AMB temperature ever reaches 110.0°C and keeps it off until the temperature drops to 109.0°C; and similarly for the DRAM temperature. The control decisions by the DTM-BW, DTM-ACG and DTM-CDVFS schemes are self explained in the table. The DTM scale indicates the difference between any two control decisions next to each other.

| Thermal Emergency Level       | L1           | L2             |       |

|-------------------------------|--------------|----------------|-------|

| AMB Temp. Range (°C)          | (-, 108.0)   | [108.0, 109.0) | DTM   |

| DRAM Temp. Range (°C)         | (-, 83.0)    | [83.0, 84.0)   | scale |

| DTM-TS: On/Off                | С            | n              | 100%  |

| DTM-BW: Bandwidth             | No limit     | 19.2GB/s       | 25%   |

| DTM-ACG: $\#$ of Active Cores | 4            | 3              | 25%   |

| DTM-CDVFS: Freq./Vol.         | 3.2GHz@1.55V | 2.4GHz@1.35V   | 25%   |

| Thermal Emergency Level       | L3             | L4                                   | L5        |

|-------------------------------|----------------|--------------------------------------|-----------|

| AMB Temp. Range (°C)          | [109.0, 109.5) | [109.5, 110.0)                       | [110.0,-) |

| DRAM Temp. Range (°C)         | [84.0, 84.5)   | [84.5, 85.0)                         | [85.0, -) |

| DTM-TS: On/Off                | On/Off         |                                      | Off       |

| DTM-BW: Bandwidth             | 12.8GB/s       | $6.4 \mathrm{GB/s}$                  | Off       |

| DTM-ACG: $\#$ of Active Cores | 2              | 1                                    | 0         |

| DTM-CDVFS: Freq./Vol.         | 1.6GHz@1.15V   | $0.8 \mathrm{GHz} @ 0.95 \mathrm{V}$ | Stopped   |

Table 4.3Thermal emergency levels and their default settings used for the<br/>chosen FBDIMM.

#### 4.3.4 Parameters in PID Formal Controller

In the PID formal controller, parameters  $K_c$ ,  $K_I$  and  $K_D$  are generally obtained by heuristics and/or performance tuning. We use performance tuning and choose the following values:  $K_c = 10.4$ ,  $K_I = 180.24$ , and  $K_D = 0.001$  for AMB, and  $K_c = 12.4$ ,  $K_I = 155.12$  and  $K_D = 0.001$  for DRAM. This approach is used in a previous study [52]. The PID controller's target temperatures of the AMB and DRAMs are 109.8 and 84.8°C, respectively. In our FB-DIMM configuration, the setting leads to quick settling time and guarantees that the thermal limits will not be exceeded. To avoid the saturation effect [52, 9] created by the integral factor, we only turn on the integral factor when the temperature exceeds a certain threshold, 109.0°C for the AMB and 84.0°C for the DRAM by default; the integral factor is frozen when the control output saturates the actuator, which can effectively make the PID controller to respond quickly to temperature changes.

## 4.4 Effectiveness of Memory DTM Schemes

We use the isolated DRAM thermal model described in Section 3.4 for performance, power and energy evaluation of DTM schemes in this section.

## 4.4.1 Performance Impact of Thermal Release Point

With DTM-TS, when the temperature exceeds the TDP (thermal design point), thermal management mechanisms are triggered; after the temperature drops below the TRP (thermal release point), the mechanisms are disabled. For a given system, the choice of TRPs affects the degree of performance loss due to thermal management. According to the FBDIMM specification [23], the TDPs of AMB and DRAM chips are 110.0°C and 85.0°C, respectively, for the FBDIMM that we choose. In this section, we will first study the performance impact of TRPs in DTM-TS. The other schemes use more levels of thermal thresholds, and adjusting the thresholds shows similar impact.

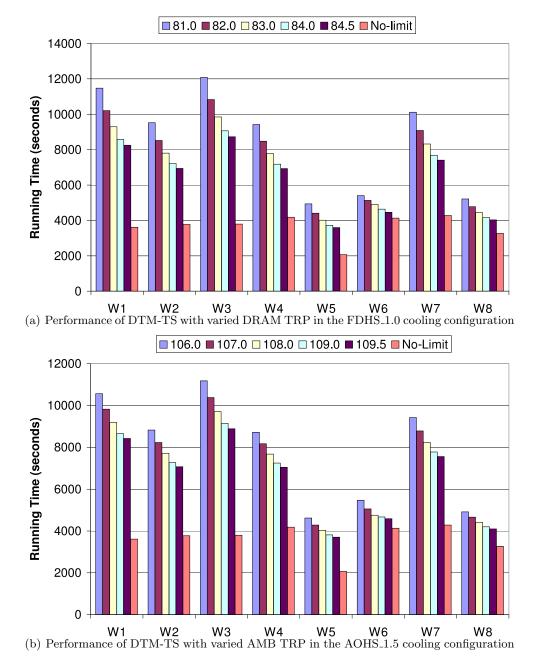

Figure 4.2 shows the running time of workloads using DTM-TS with different TRP values under FDHS\_1.0 (Full DIMM Heat Spreader with air velocity 1.0m/s) and AOHS\_1.5 (AMB

Figure 4.2 Performance of DTM-TS with varied TRP. The DRAM TDP is 85.0°C and the AMB TDP is 110.0°C.

Only Heat Spreader with air velocity 1.5m/s) configurations. For comparison, the performance of an ideal system without any thermal limit (No-limit) is also presented. In the FDHS\_1.0 configuration, the DRAMs usually enter thermal emergency before the AMBs, therefore we only vary the DRAM TRP. In the AOHS\_1.5 configuration, the AMBs usually enter thermal emergency first, therefore we only vary the AMB TRP.

As shown in the figure, the performance loss due to thermal emergency is large. The running time of DTM-TS is up to three times of that without thermal limit. As expected, a higher TRP value causes smaller performance loss. For instance, compared with no thermal limit, the execution time of workload W2 is increased by 152% when the DRAM TRP is 81.0°C under FDHS\_1.0, and the increase drops to 84% when the DRAM TRP is 84.5°C. A higher TRP value allows the system to stay at normal execution mode longer. In addition, the falling speed of temperature decreases as the temperature drops since the difference between the device and ambient temperatures is narrowing. As a result, high TRP values are desirable for performance purpose. However, we cannot set the TRP value of a component too close to its TDP value due to imperfect thermal sensors and delay on sensor reading. Thus, in the rest of experiments, we set the TRP values to 109.0°C for AMB and 84.0 for DRAM chips, respectively (1.0°C from their corresponding TDP values).

## 4.4.2 Performance Comparison of DTM Schemes

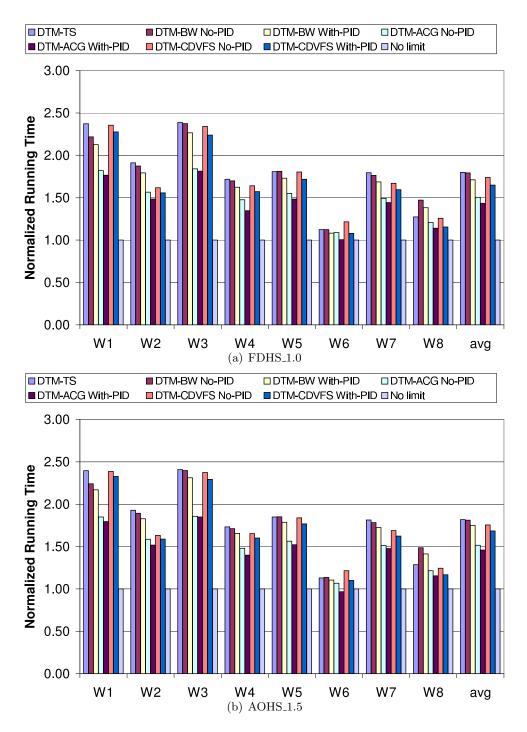

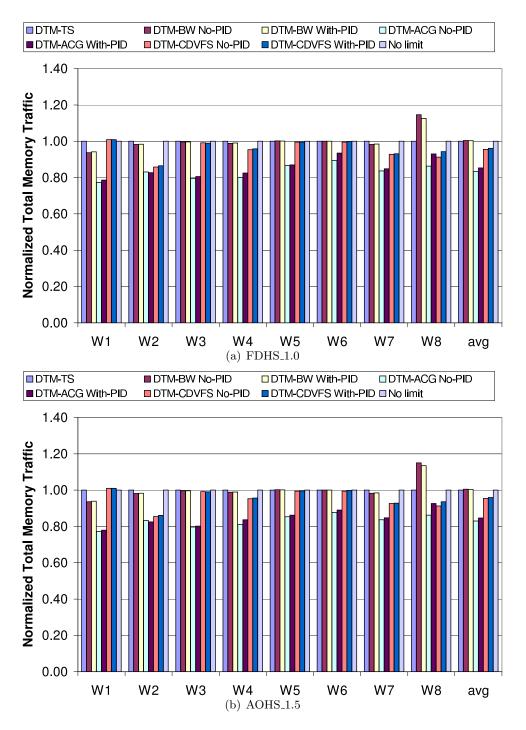

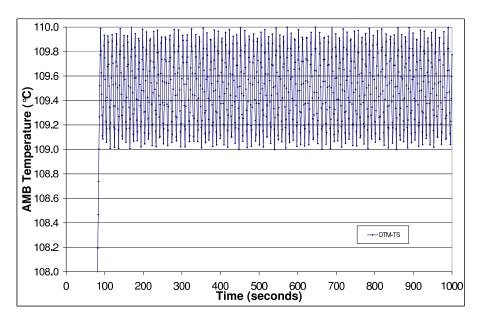

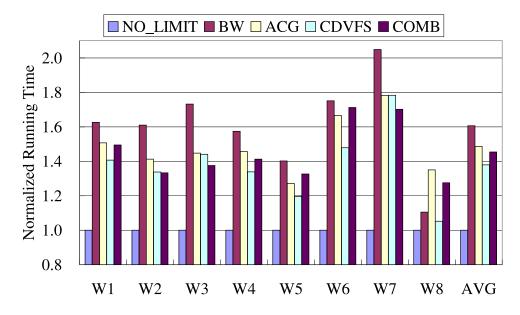

**Running Time** Figure 4.3 presents the running time of the DTM schemes normalized to that of the ideal system without thermal limit. We do not present the data of DTM-TS with PID (the formal control method) because DTM-TS has only two control decisions and we find it does not benefit from the PID approach. The figure shows that the choice of DTM schemes affects the performance significantly: The normalized running time ranges from 0.97 to 2.41. Notice that all DTM schemes avoid thermal risk; and shorter running time means better performance.

The proposed DTM-ACG scheme has much better performance than DTM-TS and DTM-BW techniques; and the proposed DTM-CDVFS scheme is moderately better than those two.

Figure 4.3 Normalized running time for DTM schemes.

The use of PID further improves the performance of DTM-ACG, DTM-CDVFS and DTM-BW. With the AOHS\_1.5 configuration, the average normalized running time of DTM-TS and DTM-BW is 1.82 and 1.81. DTM-ACG and DTM-CDVFS improve it to 1.52 and 1.75, respectively. The use of PID further improves it to 1.75, 1.46 and 1.68 for DTM-BW, DTM-ACG and DTM-CDVFS schemes, respectively. The performance with the FDHS\_1.0 cooling package has a similar trend.

Under AHOS\_1.5, the DTM-BW scheme has almost the same performance as DTM-TS. Compared with DTM-TS, DTM-ACG without PID can improve performance by up to 29.6% (for workload W1) and 18.5% on average; and DTM-CDVFS without PID can improve performance by up to 18.1% (for W2) and 3.6% on average. Combined with the PID method, the maximum performance improvement of DTM-ACG and DTM-CDVFS is 33.5% and 21.4%, respectively; and their average performance improvement is 23.4% and 8.3%, respectively. We will analyze the sources of performance gains in following discussion. It is worth noting that the performance of W6 when using DTM-ACG, combined with PID, is even better than that without thermal limit. A major reason is that the L2 cache conflicts drops when ACG is applied (miss rate dropping from 69.0% to 64.7% under AHOS\_1.5).